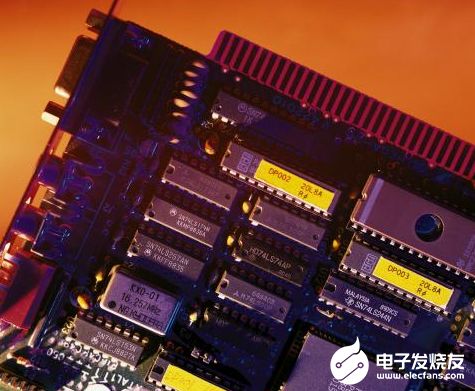

据TechInsights更新的2024年第二季内存技术路线图显示,三星和SK海力士已将D1a和D1b单元设计的产品商业化,包括DDR5、LPDDR4X、LPDDR5和LPDDR5X,采用最小的12纳米级DRAM单元设计。两家公司都率先采用EUV光刻技术,年原厂技术最新进展而美光科技则继续采用基于ArF和ArFi的图案化技术直至其1α和1β代,并计划在1γ代中引入EUV。三星在D1a和D1b代中将EUV光刻扩展到五个或更多掩模。SK海力士遵循类似的EUVL策略,已在D1a和D1b代中采用该策略,并计划在未来几代中增加EUVL步骤。

HKMG技术正变得越来越流行。三星首先在D1xGDDR6芯片中使用HKMG作为外围结构,并将其扩展到D1yDDR5芯片。美光已在D1z图形DRAM中使用HKMG,并将其扩展到D1β一代的所有DRAM类型。SK海力士在D1y和D1aGDDR6中并入了HKMG,最近又在D1bDDR5设备中加入了HKMG。

南亚科、华邦电和力积电等台湾制造商提供30纳米和20纳米级DRAM产品。

明年初,主要厂商将发布D1c量产DRAM,随后将在2026年或2027年推出最终的10纳米级DRAM器件(D1d或D1δ节点)。到2030年,DRAM技术预计将缩小到单晶数字纳米节点,具有0a、0b、0c或0α、0β和0γ代。三星正在开发VS-CAT和VCT3DDRAM,而SK海力士和美光则专注于垂直堆叠DRAM。DRAM技术的未来看起来充满希望,将满足高性能应用和新兴技术日益增长的需求。

免责声明:本网站部分内容由用户自行上传,若侵犯了您的权益,请联系我们处理,谢谢!联系QQ:2760375052